# AN10348

PIP212-12M Design Guide

Rev. 01 — 13 January 2005

Application note

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | PIP212, Point of Load, VRM (Voltage Rectifier Module), buck converter                                                                                                                                                                                                                                                                                                                                    |

| Abstract | The Philips Intelligent Power PIP212-12M is a fully integrated output stage for high current synchronous buck regulators. The PIP212-12M incorporates the functionality of three devices: a MOSFET driver, a control MOSFET and a synchronous MOSFET. This design guide provides an overview of the PIP212-12M along with design and layout techniques to obtain optimal performance from your solution. |

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 01  | 20050113 | Initial version |

## **Contact information**

For additional information, please visit: <u>http://www.semiconductors.philips.com</u>

For sales office addresses, please send an email to: <a href="mailto:sales.addresses@www.semiconductors.philips.com">sales.addresses@www.semiconductors.philips.com</a>

AN10348

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

### 1. Introduction

The Philips Intelligent Power (PIP) devices are fully integrated solutions for the output stages of high current synchronous buck regulators. The PIP212-12M is targeted for use in switching power supplies, voltage regulators, and point of load converters (on board and module designs). The performance of the PIP212-12M makes it the optimal solution for powering advanced microprocessors, high current DSP, DDR memory systems and ASIC devices.

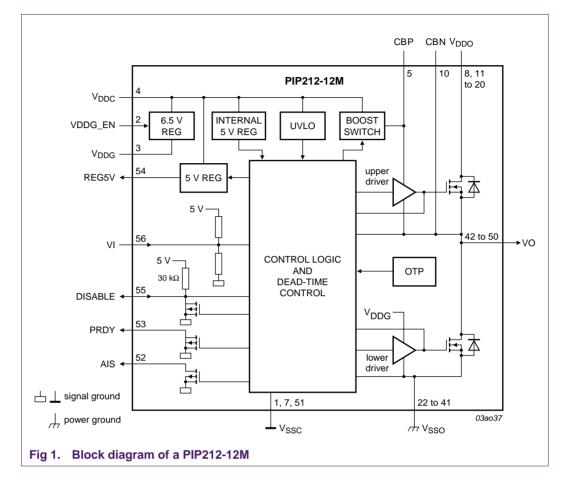

The PIP212-12M consists of a high side (control FET), low side (synchronous FET), and a FET driver. Contained in a single surface mount package with integral heat sink, the fully integrated device greatly simplifies the design and layout of single and multi-phase buck regulators.

The PIP212-12M has been designed with high performance MOSFETs and customized driver for superior efficiencies. The driver has been designed to monitor switching dead time and actively eliminate dead time without allowing the devices to go into cross conduction. Efficiencies of greater than 90% can be realized due to the optimized internal design.

An extensive feature set allows designers to easily and flexibly adapt this part to their specific requirements without additional circuitry. The feature set includes functionality for sequencing, onboard regulator for providing 5 V power in 12 V only applications, built in loss phase detection circuitry for multiphase applications, and Vo sense to allow current sense back to the PWM. This feature allows multi-phase current sharing designs.

The integrated design allows the PIP212-12M to be used as the building block of buck regulators capable of greater than 30 Amperes per phase and frequencies of up to 1MHz per phase with greater power densities than are possible with discrete solutions or previous integrated solutions.

#### **1.1 Typical buck circuit utilizing the PIP212-12M**

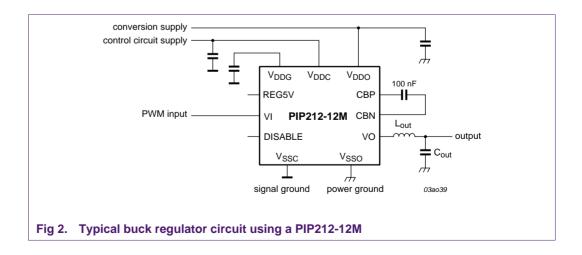

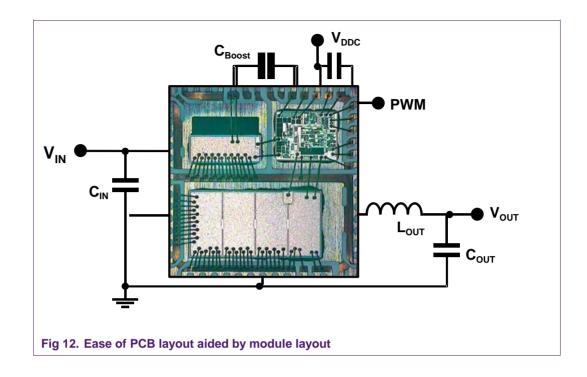

Using the PIP212-12M device, as a building block for a buck regulator requires minimal external components, as can be seen in the typical buck regulator circuit shown in figure 2. The only additional external components required are the addition of a PWM controller IC, external inductor, input and output capacitors, and a small external boost capacitor.

### 2. Package description and connections

The PIP212-12M is packaged in a low profile (8 x 8 x 0.85 mm), 56 pin Heatsinked, Very thin, Quad, Flat, No leads, (HVQFN) package. The HVQFN package is the Philips equivalent to the Amkor MicroLeadFrame (MLF) package. The leadless package has 56 perimeter lands (pins) and an additional three separate large pads on the bottom side of the package. The pads (which are electrically connected to many of the 56 perimeter pins) act as large electrical connections to minimize connection impedances for the driver, control FET, and synchronous FET and to provide an excellent thermal connection from junction to PCB of less than 4 °C/W. The pins and pads that are connected are as follows:

- Driver power ground, V<sub>ssc</sub>, (PAD 1 and PINS 1, 7, 51)

- Output stage (conversion) power, V<sub>DDO</sub>, (PAD 2 and PINS 8, 11-20)

- Output (switch) node, VO, (PAD 3 and PINS 42-50)

The pad and their corresponding pins should be connected on the layout for optimal electrical and thermal performance. The remaining 56 perimeter lands or pins provide the additional electrical connections required by the PIP212-12M. These pins have been clustered together in groups to provide common high current low inductance electrical connections to the PIP212-12M. For detailed pin descriptions refer to the PIP212-12M data sheet.

The driver power  $V_{DDC}$ , and conversion input power,  $V_{DDO}$ , are kept separate and have independent ground connections,  $V_{SSC}$  and  $V_{SSO}$ , respectively.  $V_{DDC}$  and  $V_{DDO}$  could be provided from the same supply as long as the driver power,  $V_{DDC}$  is filtered via an RC network. The driver ground ( $V_{SSC}$ ) and output stage supply ground ( $V_{SSO}$ ) must be grounded separately as shown in Section 4, "Layout considerations".

The PWM input connection, **VI**, takes a logic level input from any industry standard single phase or multiphase PWM controller and controls the switching of the control and synchronous FETs. When the PWM signal is high, the control FET is switched "on" and the synchronous FET is switched "off". When the PWM is low, the control FET is switched "off" and the synchronous FET is switched "on". A tri-state input (floated PWM output) to **VI** pin will cause both the control and synchronous FETs to be switched off.

There are several functions available to enhance control, reliability and sequencing:

- UnderVoltage LockOut (UVLO) is implemented internally in the PIP212-12M. The UVLO circuitry monitors the power provided to controller (VDDC). When this voltage is below a certain threshold, operation of the PIP is disabled. The DISABLE pin is internally held low and both MOSFETs are off. The Power-Ready (PRDY) flag indicates the status of the UVLO. The PRDY flag is an open drain output that is pulled low whenever V<sub>DDC</sub> is below the UVLO threshold. This flag can be used in association with a PWM controller-enable function to ensure that the PWM is not enabled until power to the PIP is good. This is a good way to ensure that the PWM controller does not go through a soft start sequence until all power has come up to adequate levels.

- **OverTemperature Protection (OTP)** senses the die temperature and will shut down the PIP212-12M in the event that the internal threshold is exceeded. When this occurs the internal threshold, both MOSFETs are turned off and the internal  $V_{DDG}$  regulator is shut down. This functionality protects the PIP212-12M device from being damaged in unexpected operating conditions such as excessive ambient

temperatures or if the output currents exceed those intended in the design application.

- The Am I Switching (AIS) pin is a fault flag that can be used to implement lost phase detection. Lost phase detection is used in multiphase applications to ensure that a failed phase is detected instead of the remaining phases picking up the additional load and the fault being undetected. The AIS flag looks for voltage transients on the  $V_0$  pin. During normal operation, if no voltage transients have occurred on the  $V_0$  pin for approximately 40  $\mu$ s, the AIS pin is pulled low. False signals during start-up are prevented by internally activating this function 200  $\mu$ s after either the DISABLE pin becoming high or the driver leaving the 3-state mode.

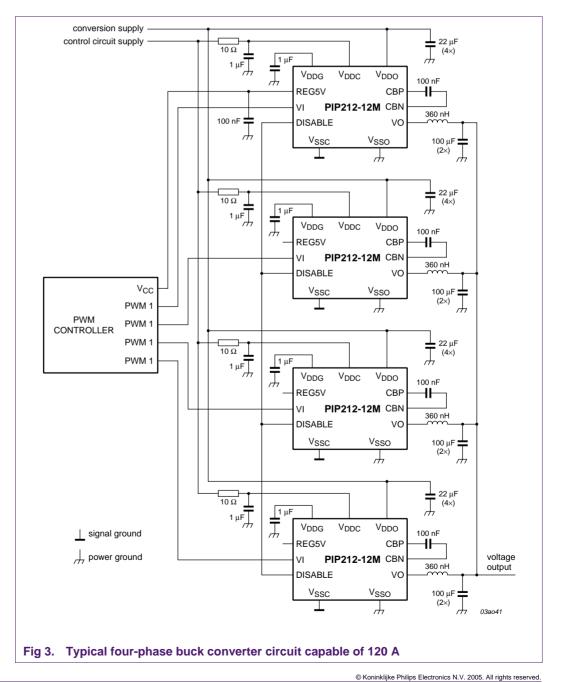

- The DISABLE pin is used to shut down the PIP212-12M externally. Pulling the DISABLE pin low turns off both MOSFETs, disables the REG5V output and makes the AIS flag open drain. The DISABLE pin is pulled high via an internal pull up resistor, but is internally held low until the UVLO threshold is exceeded. The PIP212-12M will enable itself once the UVLO is exceeded as long as an external source does not pull it low. In multiphase designs this pin should be connected to all other PIP212-12M DISABLE pins and thus ensure that all PIP12-12M devices remain off until all of the PIP212-12M have exceeded the UVLO threshold. See Figure 3.

- The **REG5V function** provides a low current regulated 5V output when both PRDY and DISABLE are high. It can supply power to a PWM controller or as part of an enable function for a PWM controller. Using this pin to power the PWM controller is another way to ensure that the PWM controller does not start up and go through a soft start sequence until all the PIP212-12Ms are operational.

- The PIP212-12M also features a **3-state input function**. If the PWM controller output goes high impedance, the input to this pin will be driven to nominally 2.5 V by an internal voltage divider of the PIP212-12M. This voltage is between the V<sub>IH</sub> and the V<sub>IL</sub> level. If the voltage on this pin remains between these levels for a period longer than the td(3-state), both MOSFETs are turned off. This function is used by PWM manufacturers to protect against faults such as an overvoltage fault.

#### 2.1 V<sub>DDG</sub> power options

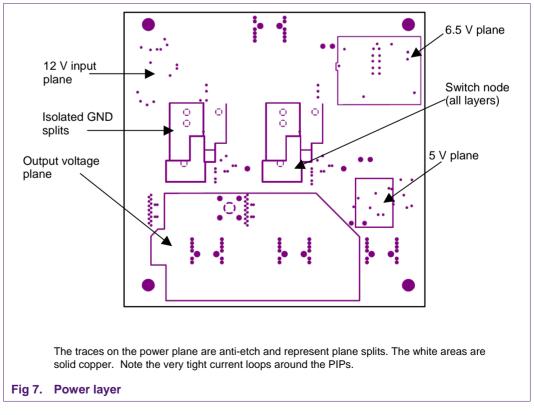

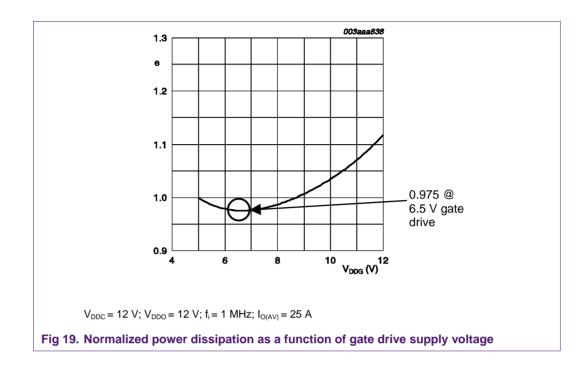

An external pin, **V**<sub>DDG</sub>, is used to supply power to the lower gate drive. The voltage to this pin should be between 5 V and 12 V, and can be adjusted for optimal efficiency depending on the application, as shown in Figure 9 of the PIP212-12M data sheet,  $V_{DDC} = 12 \text{ V}$ ,  $V_{DDO} = 12 \text{ V}$ ,  $f_i = 1 \text{ MHz}$ , and  $I_{O(AV)} = 25 \text{ A}$ , the optimal value is 6.5 V. In most 12 V applications, a value of 6.5 V will provide optimal efficiency.

For ease of design in applications that do not have access to an external supply, an internal linear regulator will supply this 6.5 V to the  $V_{DDG}$ . Leaving the VDDG\_EN pin open enables the internal  $V_{DDG}$  regulator. If an external supply is to be connected to  $V_{DDG}$  then the VDDG\_EN pin must be connected to the  $V_{SSC}$  to disable the  $V_{DDG}$  regulator and 1uF capacitor should be connected to the  $V_{DDG}$  pin. Note that for minimum power loss, the use of an external 5 V supply is preferred to using the internal  $V_{DDG}$  regulator.

### 3. Multiphase operation

The PIP212-12M device is ideally suited for multiphase operation. The reduced component count and ease of layout make multiphase designs much easier to implement. Efficient high frequency operation minimizes the number of output capacitors required and can also allow replacement of electrolytic capacitors by ceramic capacitors. This reduces the total PCB area required to support large continuous output currents and larger current transients. A typical four-phase solution is shown below.

Philips has applied the PIP212-12M in applications from one to four phases and demonstrated currents up to 30 A per phase when converting down from 12 V to 1.2 V at an operating frequency of 500 kHz.

### 4. Layout considerations

The PIP212-12M greatly simplifies the layout of a buck converter, as it is a single building block instead of three components (driver, control FET, synchronous FET). For optimal performance, as in any power supply design, a number of elements must be considered when routing the PCB.

#### 4.1 Recommended layout

The 56 perimeter lead lands and three large pads on the package bottom side are rectangular in shape and serve as both electrical and thermal connections. Land patterns corresponding to the pins and pads are made on the PCB and standard re-flow processes are used to solder the package to the motherboard.

In order to take full advantage of the thermal and electrical benefits the HVQFN package has to offer, the PCB should have features to provide adequate power and grounding connections to minimize noise as well as effectively conduct heat away from the device.

#### 4.1.1 Noise and spikes

Noise and spikes are created due to high di/dt and/or dv/dt occurring in the presence of package and board parasitics. The main areas of concern are therefore:

- V<sub>DDO</sub> input cap Control FET (di/dt)

- Control FET Switch node (di/dt)

- Switch node (dv/dt)

- Switch node sync FET (di/dt)

- Sync FET V<sub>DDO</sub> input Cap (di/dt)

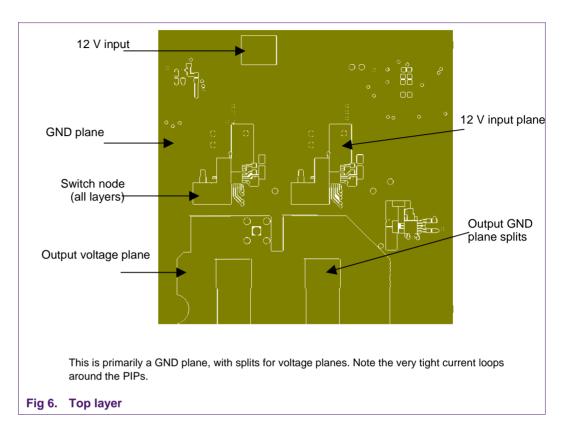

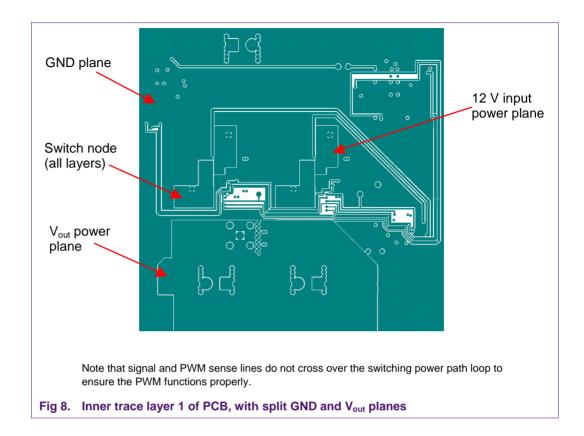

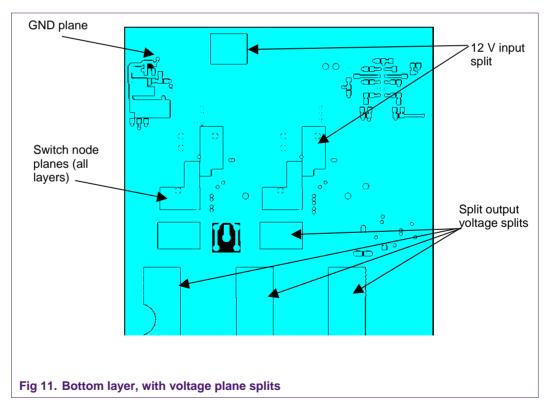

This is effectively the switching power path comprising the current loop from the input capacitor through the power MOSFETs and back to the input capacitor. For the high current path, the connections need to be as short and wide as possible to reduce ringing. *Eliminating any overlap of these planes with any others reduces capacitive parasitics.* Isolation of the  $V_{DDO}$  & power Gnd ( $V_{SSO}$ ) will prevent transmission of noise along the planes to the output.

#### 4.1.2 Typical layout

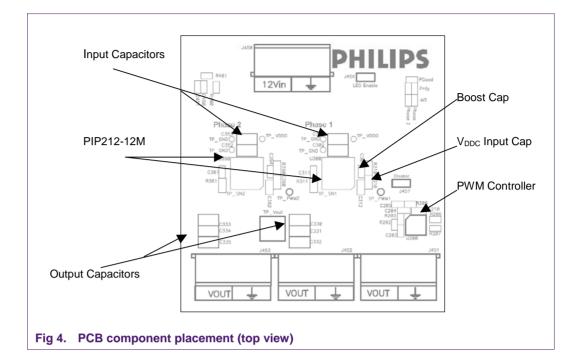

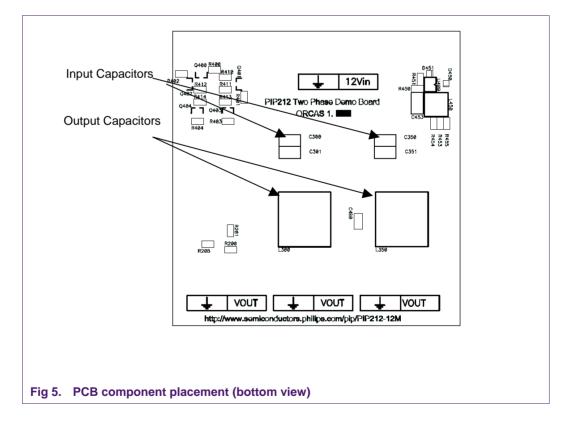

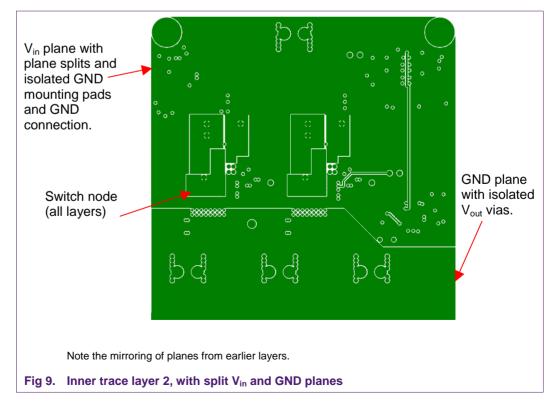

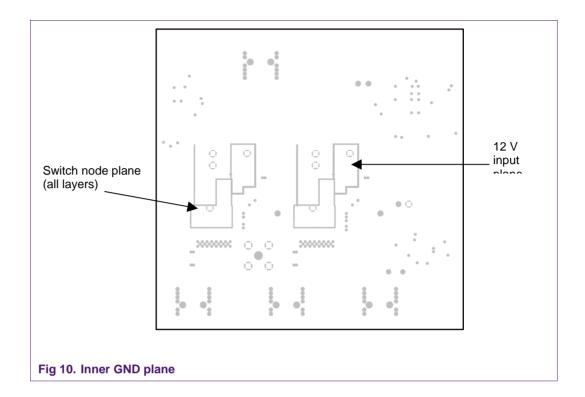

A typical layout of the part is shown in figures 4-11. The images are from a Philips 2phase demonstration board, and show applicable principles. A few key features of this layout are important to obtain optimal performance from the PIP.

- 1. The parasitic inductance of the  $V_{DDC}$  power input to the PIP212 should be minimized. Placing the  $V_{DDC}$  filter capacitor as close as possible to the PIP212 and using the widest and shortest possible PCB connections can achieve this. Pin-out of the PIP212-12M facilitates this as shown in Figure 12.

- 2. The parasitic inductance of the  $V_{DDO}$  power input to the PIP212 should be minimized. This can be achieved by minimizing the loop length between the  $V_{DDO}$  and  $V_{SSO}$  connections to the PIP212. Pin-out of the PIP212-12M facilitates this as shown in Figure 12.

- 3. The parasitic inductance of the boost capacitor loop should be minimized by placing the boost capacitor as close as possible to the PIP212. Pin-out of the PIP212-12M facilitates this as shown in Figure 12.

- 4. Expand the copper planes to the high current connections (especially the three large pads under the part) as far around the PIP212-12M device as possible. This will

reduce the I<sup>2</sup>R losses and allow large areas for conductive cooling. Mirror these copper areas as much as possible on the other layers of the board.

- 5. Incorporating thermal vias on the V<sub>DDO</sub> and V<sub>o</sub> main pads on the PCB will also greatly improve the thermal performance. While the thermal pad provides a solderable surface on the top surface of the PCB (to solder the package die pad on the board), thermal vias are needed to provide a thermal path to inner and/or bottom layers of the PCB. An array of thermal vias with a 1.0 to 1.2mm pitch and via diameter of 0.3 to 0.33 mm is recommended for the two main pads mentioned above. Solder masking is also required for thermal vias to prevent solder wicking inside the via during reflow, thus taking the solder away from the interface between the package die paddle and thermal pad on the PCB. The solder mask diameter should be 100 microns larger than the via diameter. The vias can be plugged or tented with solder mask, either from the bottom or the top surface of the PCB.

- 6. In addition to vias under the part, vias in the main copper areas will also allow for heat transfer into the other layers. Care must be taken when adding these vias, as too many vias will tend to reduce the total copper conduction area and increase the I<sup>2</sup>R losses in the conduction plane.

- 7. Fill unused areas and layers with copper to help increase the board's thermal mass and add more conduction area.

- 8. Use as thick as possible copper layers (1 oz =  $35 \mu m$  or 2 oz =  $70 \mu m$ ).

- Maintain adequate distance between heat generating sources. Key heat generating sources in a typical multi-phase buck converter are the output inductors and other PIP212-12M devices. Selecting this distance will require characterizing and understanding the thermal environment on the PCB.

For more information and detailed PCB design, board mounting, and rework guidelines refer to "*Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages*" which can be found on the Philips PIP212-12M web page.

AN10348 Application note

## 5. Electrical and thermal performance

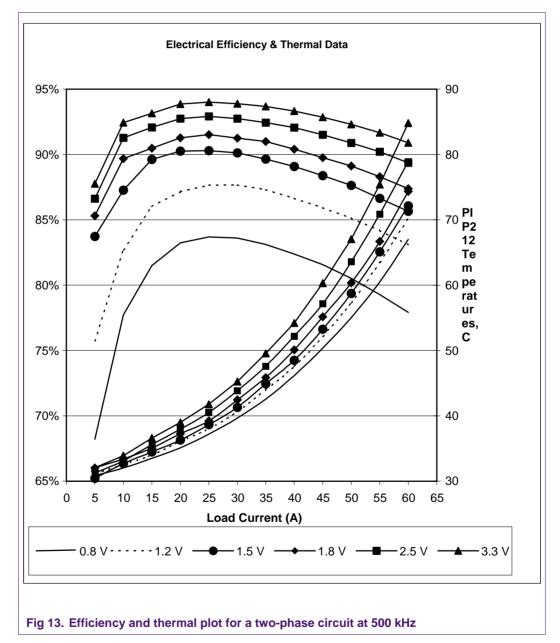

The PIP212-12M has been developed to allow designers to easily achieve highly efficient designs. As noted previously, Philips has applied the PIP212-12M in applications from one to four phases. Using layout rules as discussed in the previous section including thermal considerations, Figure 13 shows measured efficiencies and thermal data for a two-phase circuit converting down from 12 V input and operating at 500 kHz per phase, with 200 linear feet per minute (LFM) airflow across the board. The only changes to the circuit to obtain this data were to the voltage divider that established output voltage.

The thermal environment constrains the maximum performance that can be achieved from a given design solution. Using the <u>Section 4</u> guidelines on a four layer FR4 board

with thermal vias and a minimal foot print of 25 x 25 mm copper area, typical junction to ambient thermal resistances of 12 K/W can be achieved.

#### 5.1 Typical design and performance

A typical thermal design should make use of the power loss data in the data sheet. To calculate the power loss for a certain set of operating conditions, first determine the power loss for the required output current and then multiply this value by the relevant normalization factor for conditions that deviate from the default conditions used in the PIP212-12M data sheet. The following example describes this process.

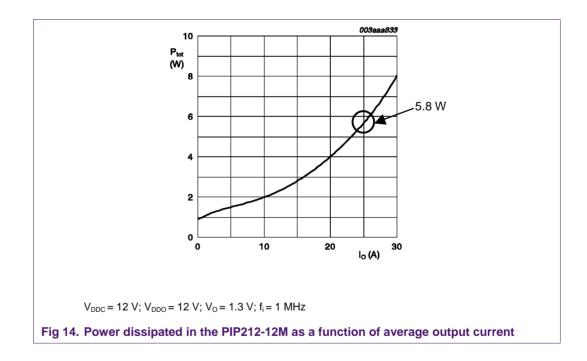

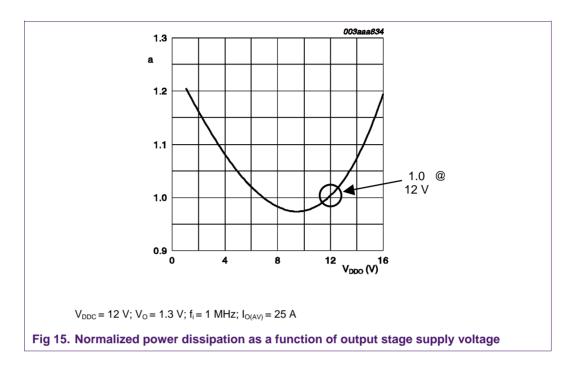

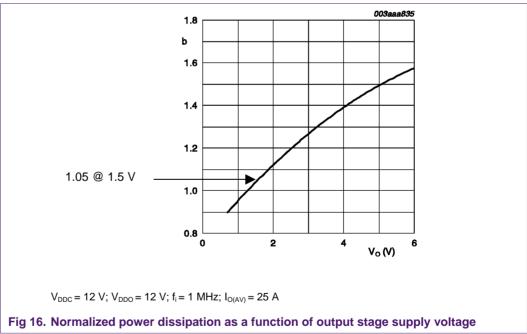

For a design with a 12 V input voltage, a 1.5 V output voltage, a switching frequency of 500 KHz and an output current per PIP212-12M of 25 A, the total power dissipation is calculated to be 4.63 W as shown below:

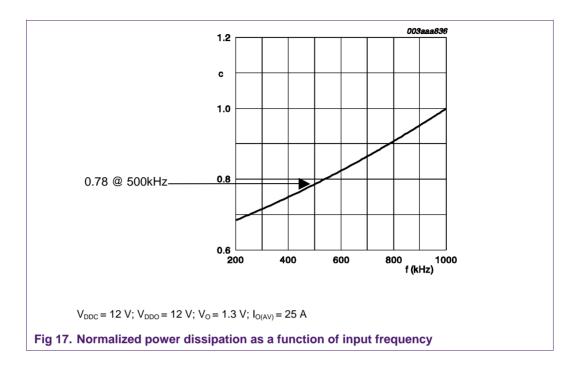

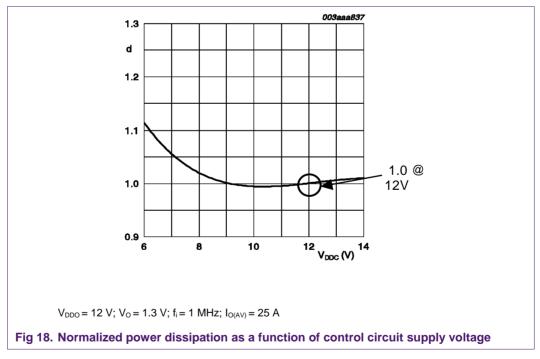

$P_{tot} = P_{d(Fig.14)} \times F_{Vddo(Fig.15)} \times F_{Vo(Fig.16)} \times F_{Freq(Fig.17)} \times F_{Vddc(Fig.18)} \times F_{Vddg(Fig.19)} =$ (1) 5.8W × 1.0 × 1.05 × 0.78 × 1.0 × 0.975 = 4.63W

The normalization factors used in the above formula have been taken directly from the data sheet power loss curves as shown below. These curves are only reproduced fro the purposes of this example, please consult the latest PIP212-12M data sheet when calculating power loss.

### 6. Summary

The PIP212-12M greatly simplifies the design and layout of the output stage of a buck converter. The small single package allows very dense, low profile designs to be achieved. Integration of the components into a single package reduces the design effort as optimization of the driver and FETs is incorporated as part of the design of the PIP212-12M. The PIP212-12M is also optimized for thermal performance with large underside pads for efficient transfer of heat to the PCB and the thin top plastic coating allowing for easy heat sinking to ambient. The efficient design and superior thermal performance enables high system efficiencies with switching frequencies up to 1 MHz and output currents greater than 30 A. By following a few basic design and layout guidelines, the optimal performance of the PIP212-12M can easily be realized in a design that meets ever-more demanding application requirements.

### 7. Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### 8. Contents

| 1.    | Introduction                                  | 3  |

|-------|-----------------------------------------------|----|

| 1.1   | Typical buck circuit utilizing the PIP212-12M | 4  |

| 2.    | Package description and connections           | 5  |

| 2.1   | V <sub>DDG</sub> power options                | 6  |

| 3.    | Multiphase operation                          | 7  |

| 4.    | Layout considerations                         | 8  |

| 4.1   | Recommended layout                            | 8  |

| 4.1.1 | Noise and spikes                              |    |

| 4.1.2 | Typical layout                                | 8  |

| 5.    | Electrical and thermal performance            | 15 |

| 5.1   | Typical design and performance                | 16 |

| 6.    | Summary                                       | 19 |

| 7.    | Disclaimers                                   | 20 |

| 8.    | Contents                                      | 21 |

© Koninklijke Philips Electronics N.V. 2005

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Date of release: 13 January 2005 Document number: AN10348